APIC Note

Motivation

This note is the learning note combining intel software developer manual[1] and other blogs. It intends to guide KVM code comprehension.

Local and IO APIC overview

- Locally connected I/O devices: local interrupts pins (LINT0 & LINT1)

- Externally connected I/O devices: I/O APIC

- Inter-processor Interrupts: IPI which is used for software self-interrupts, interrupt forwarding or preemptive scheduling

- APIC Timer Generated Interrupts: high resolution timer

- Proformance Monitoring Counter Interrupts: PMI

- Thermal Senser Interrupts: thermal sensor tripped

- APIC Internal Error Interrupts: such as accessing unimplemented register

Interrupt source is marked in Local Vector Tabe (LVT).

IPIs is generated by setting Interrupt Command Register (ICR) on system bus or APIC bus.

System Bus vs APIC Bus

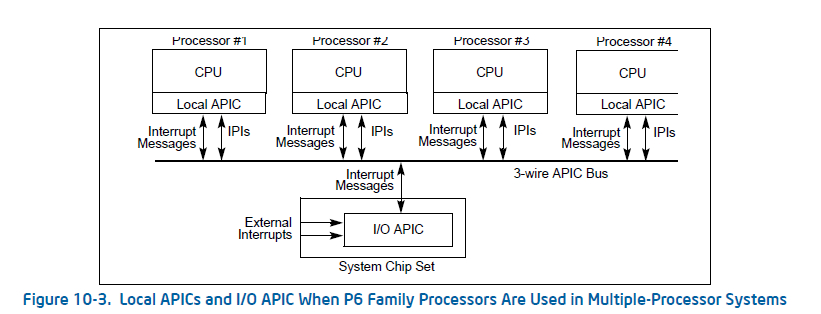

For P6 family and Pentium Processors, IOAPIC connects lapic with 3-wire inter-APIC bus.(APIC Architecture)

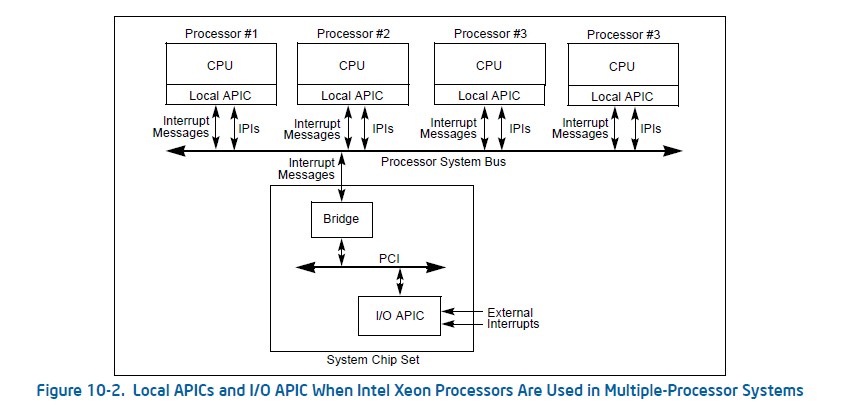

For Pentium 4 and Xeon processors, the IOAPIC connects through system bus. (xAPIC Architecuture)

Local APIC

Local APIC ID

Local APIC Version Register

Handling Interrupts

Reference

[1] Intel® 64 and IA-32 Architectures Developer's Manual: Vol. 3A